| ∀ Adders                                                                                   |        |      | <b>U.</b> J | ) (C  | ont.)           |

|--------------------------------------------------------------------------------------------|--------|------|-------------|-------|-----------------|

| v 1 Iddel 5                                                                                |        |      |             |       |                 |

| <ul> <li><u>Question</u>: How ca<br/>additions of two p<br/>using logic circuit</li> </ul> | ositi  |      | -           | -     |                 |

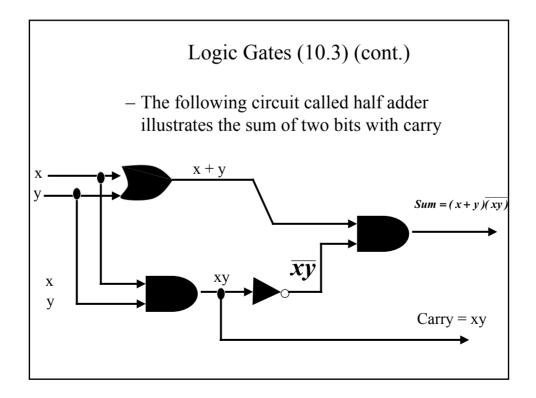

| – We first build a ci                                                                      | ircuit | that | can b       | e use | ed to determine |

| x + y where x and                                                                          | d y a  | e tw | o bits      | 5     |                 |

|                                                                                            | Input  |      | Output      |       |                 |

|                                                                                            | х      | у    | S           | с     |                 |

|                                                                                            | 1      | 1    | 0           | 1     |                 |

|                                                                                            | 1      | 0    | 1           | 0     |                 |

|                                                                                            | 0      | 1    | 1           | 0     |                 |

|                                                                                            | 0      | 0    | 0           | 0     |                 |

Ch.10 (Part 1) [Sections 10.1, 10.2, 10.3 & 10.4]: Boolean Algebra &

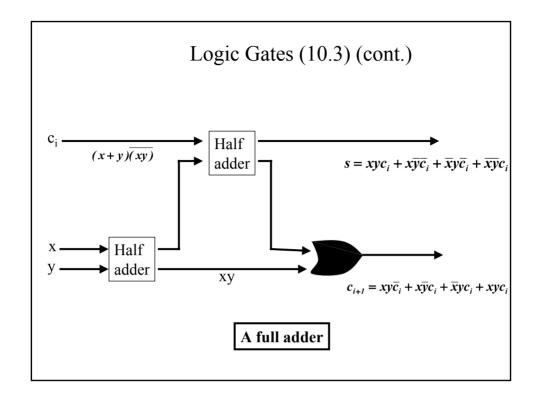

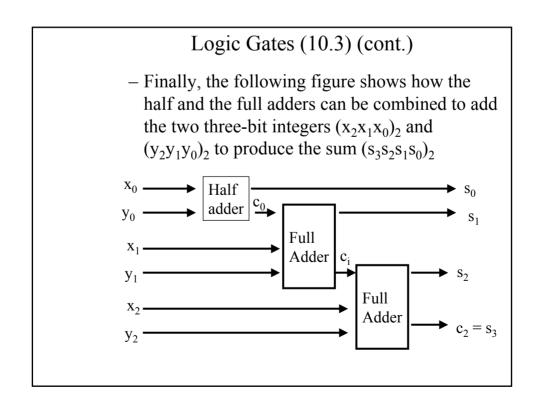

- We need to compute the sum bit and the carry bit when two bits and a carry are added

- The inputs to this full adder are the bits  $\boldsymbol{x}$  and  $\boldsymbol{y}$  and the carry  $\boldsymbol{c}_i$

- The outputs are the sum bit s and the new carry  $c_{i+1}$ .

| Input |   | Output         |   |                  |  |

|-------|---|----------------|---|------------------|--|

| х     | у | c <sub>i</sub> | s | C <sub>i+1</sub> |  |

| 1     | 1 | 1              | 1 | 1                |  |

| 1     | 1 | 0              | 0 | 1                |  |

| 1     | 0 | 1              | 0 | 1                |  |

| 1     | 0 | 0              | 1 | 0                |  |

| 0     | 1 | 1              | 0 | 1                |  |

| 0     | 1 | 0              | 1 | 0                |  |

| 0     | 0 | 1              | 1 | 0                |  |

| 0     | 0 | 0              | 0 | 0                |  |

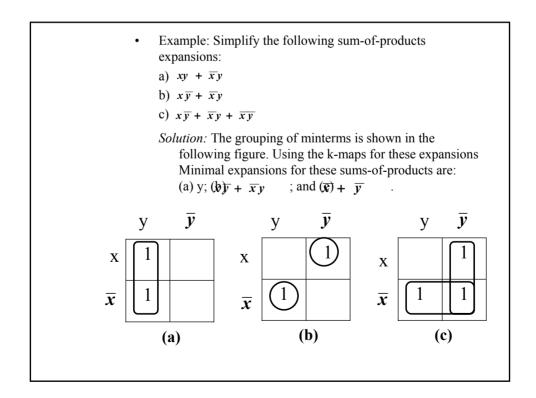

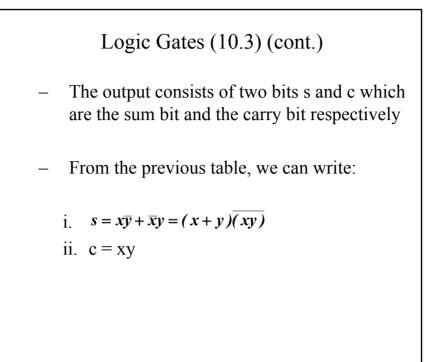

Logic Gates (10.3) (cont.)

The two outputs of the full adder, the sum bit s and the carry c<sub>i+1</sub> are given by the sum-of-products expansion xyc<sub>i</sub> + xyc<sub>i</sub> + xyc<sub>i</sub> and xyc<sub>i</sub> + xyc<sub>i</sub> + xyc<sub>i</sub>, respectively

The full adder circuit using half adders is depicted in the following picture

Ch.10 (Part 1) [Sections 10.1, 10.2, 10.3 & 10.4]: Boolean Algebra &

Ch.10 (Part 1) [Sections 10.1, 10.2, 10.3 & 10.4]: Boolean Algebra &

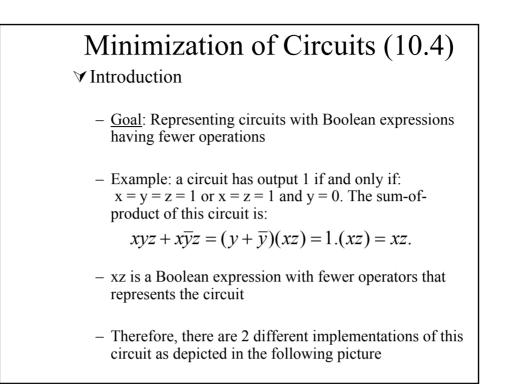

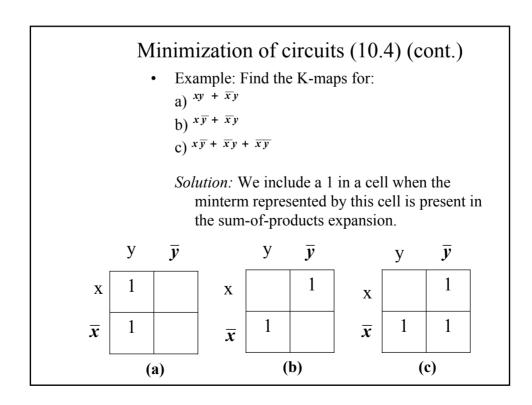

## Minimization of circuits (10.4) (cont.)

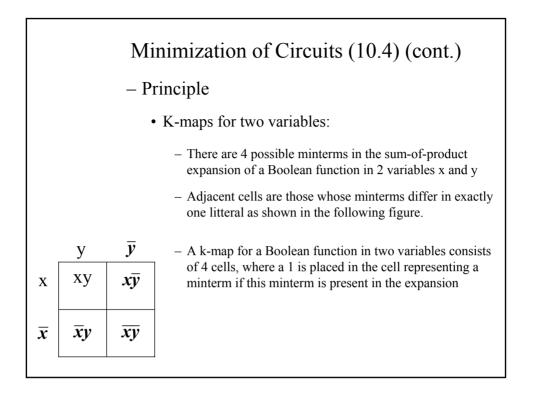

- Whenever there are 1's in two adjacent cells, the minterms are combined into a product involving just one of the variables

- We circle blocks of cells in the K-maps that represent minterms that can be combined and then find the corresponding sum of the products

- The goal is to identify the largest possible blocks, and to cover all the 1s with the fewest blocks using the largest blocks first and always using the largest possible blocks.